#### Virtual Memory

- 13 Address Spaces

- 14 Memory API

- 15 Address Translation

- 16 Segmentation

- 17 Free Space Management

- 18 Paging

- 19 Translation Lookaside Buffers

- 20 Advanced Paging

- 21 Swapping

- 22 Swapping Policy

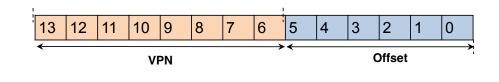

### Two-level example

| Flag             | Detail                         |

|------------------|--------------------------------|

| Address space    | 16 KB                          |

| Page size        | 64 byte                        |

| Virtual address  | 14 bit                         |

| Num pages        | $2^{14}/2^6 = 2^8 = 256$ pages |

| VPN              | 8 bit                          |

| Offset           | 6 bit                          |

| Page table entry | 4 bytes                        |

A 16-KB Address Space With 64-byte Pages

# **Inverted Page Tables**

- Keeping only a single page table that has

- an entry for each physical page of the system

- The entry tells us

- which process is using this page, and

- which virtual page that maps to this physical page

- Finding translating a virtual address now requires a search!

- But can use a per-process hash (PowerPC)

- Hash has entry for each *used* virtual/physical page, pointing to the single global page table

# Virtual Memory

- 13 Address Spaces

- 14 Memory API

- 15 Address Translation

- 16 Segmentation

- 17 Free Space Management

- 18 Paging

- 19 Translation Lookaside Buffers

- 20 Advanced Paging

- 21 Swapping and Demand Paging

- 22 Swapping Policy

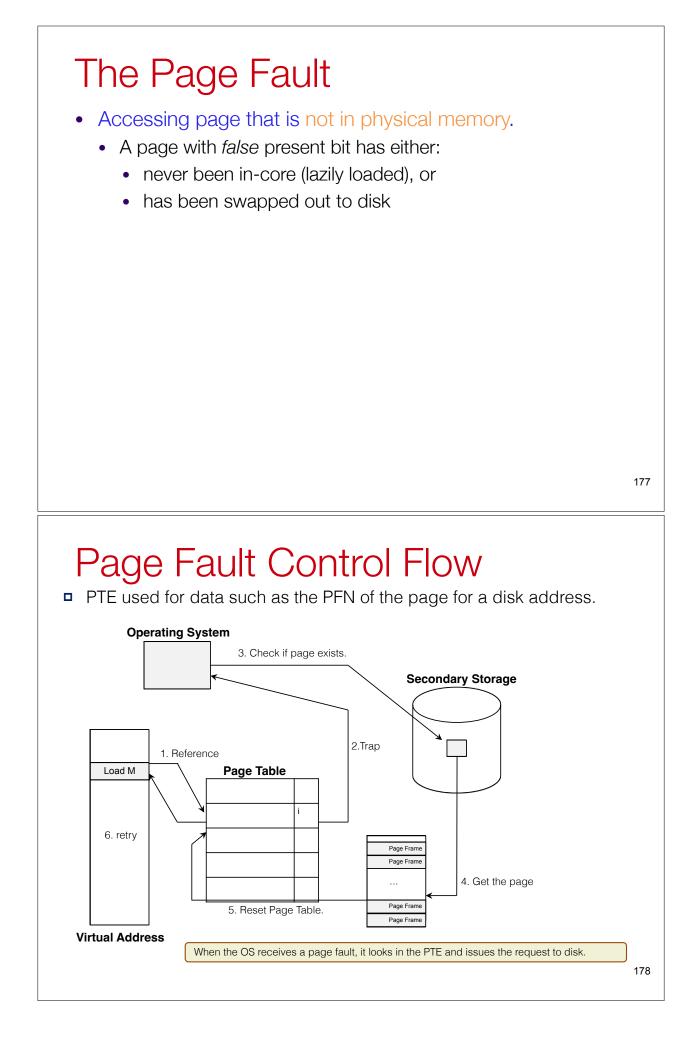

| Single-Level Page Fault hardware |                                                         |               |   |

|----------------------------------|---------------------------------------------------------|---------------|---|

| 1:                               | VPN = (VirtualAddress & VPN_MASK) >> SHIFT              |               | ] |

| 2:                               | (Success, TlbEntry) = TLB_Lookup(VPN)                   |               |   |

| 3:                               | <pre>if (Success == True) // TLB Hit</pre>              |               |   |

| 4:                               | <pre>if (CanAccess(TlbEntry.ProtectBits) == True)</pre> | no page table |   |

| 5:                               | Offset = VirtualAddress & OFFSET_MASK                   | > mem ever    |   |

| 6:                               | PhysAddr = (TlbEntry.PFN << SHIFT)   Offset             | J accessed    |   |

| 7:                               | Register = AccessMemory (PhysAddr)                      |               |   |

| 8:                               | else                                                    |               |   |

| 9:                               | RaiseException(PROTECTION_FAULT)                        |               |   |

| 10:                              | else // TLB Miss                                        |               |   |

| 11:                              | PTEAddr = PTBR + (VPN * sizeof(PTE))                    |               |   |

| 12:                              | PTE = AccessMemory (PTEAddr)                            |               |   |

| 13:                              | <pre>if (PTE.Valid == False)</pre>                      | J             |   |

| 14:                              | RaiseException(SEGMENTATION_FAULT)                      | crash?        |   |

| 15:                              | else                                                    |               |   |

| 16:                              | <pre>if (CanAccess(PTE.ProtectBits) == False)</pre>     |               |   |

| 17:                              | RaiseException (PROTECTION_FAULT)                       |               |   |

| 18:                              | <pre>else if (PTE.Present == True)</pre>                |               |   |

| 19:                              | <pre>// assuming hardware-managed TLB</pre>             |               |   |

| 20:                              | TLB_Insert(VPN, PTE.PFN, PTE.ProtectBits)               |               |   |

| 21:                              | RetryInstruction()                                      | } all good    |   |

| 22:                              | <pre>else if (PTE.Present == False)</pre>               | 1             |   |

| 23:                              | RaiseException (PAGE_FAULT)                             | j page fault  |   |

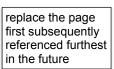

# Single-Level Page Fault software

| 1: | PFN = FindFreePhysicalPage()                                      |

|----|-------------------------------------------------------------------|

| 2: | <pre>if (PFN == -1) // no free page found</pre>                   |

| 3: | <pre>PFN = EvictPage() // run replacement algorithm</pre>         |

| 4: | <pre>DiskRead(PTE.DiskAddr, pfn) // sleep (waiting for I/0)</pre> |

| 5: | <pre>PTE.present = True // update page table with present</pre>   |

| 6: | PTE.PFN = PFN // bit and translation (PFN)                        |

| 7: | RetryInstruction() // retry instruction                           |

• The OS must find a physical frame for the soon-be-faulted-in page

◆ If no such page, run replacement algorithm (often asynchronous)

# When Replacements Really Occur

- Wait until memory entirely full?

- No, proactively try to keep small portion of memory free

- Swap or Page Daemon

- Frees/evicts page frames if fewer than a low-water threshold available

- ...until a high-water threshold pages available

# Virtual Memory

- 13 Address Spaces

- 14 Memory API

- 15 Address Translation

- 16 Segmentation

- 17 Free Space Management

- 18 Paging

- 19 Translation Lookaside Buffers

- 20 Advanced Paging

- 21 Swapping

- 22 Swapping Policy

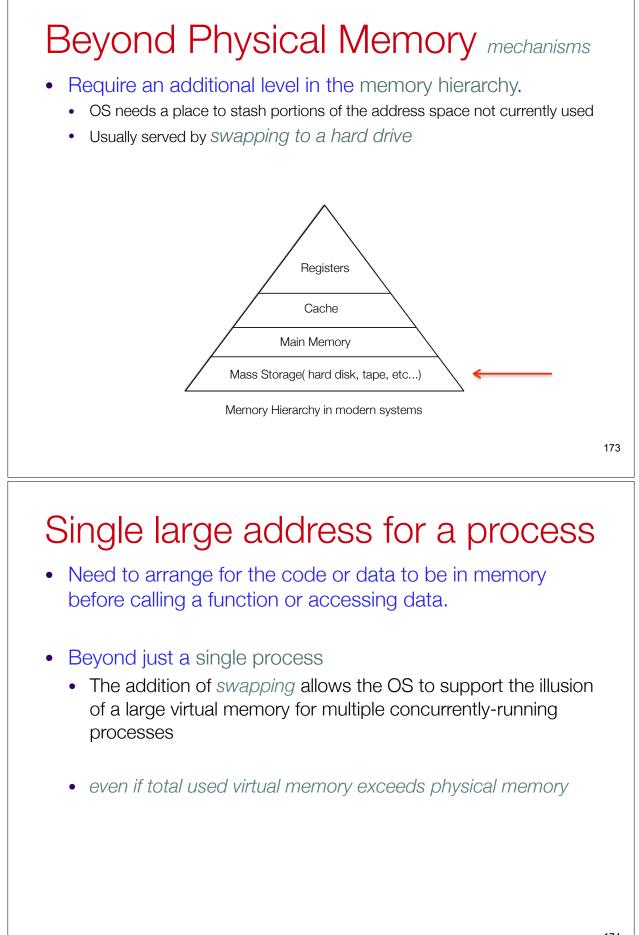

# **Beyond Physical Memory: Policies**

- <u>Memory pressure</u> forces the OS to start paging out pages to make room for actively-used pages.

- Deciding which page to <u>evict</u> is encapsulated within the replacement policy of the OS.

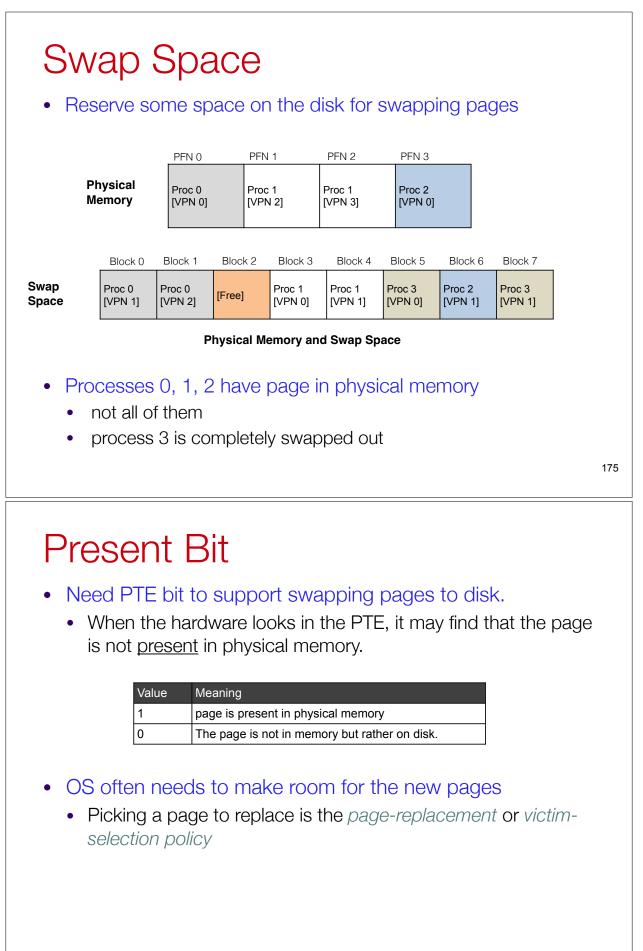

### Swap Management

- Goal in picking a replacement policy for this *cache* is to minimize the number of cache misses.

- The number of cache hits and misses let us calculate the *average memory access time (AMAT)*.

| $AMAT = T_M +$ | $P_{miss} * T_D$ |

|----------------|------------------|

|----------------|------------------|

| Argument          | Meaning                                                      |  |

|-------------------|--------------------------------------------------------------|--|

| $T_M$             | The cost of accessing memory                                 |  |

| $T_D$             | The cost of accessing disk                                   |  |

| P <sub>hit</sub>  | The probability of finding the data item in the cache(a hit) |  |

| P <sub>miss</sub> | The probability of not finding the data in the cache(a miss) |  |

#### The Optimal Replacement Policy OPT

- · Leads to the fewest number of misses overall

- Replaces the page that will be accessed furthest in the future

- Resulting in the fewest-possible cache misses

- Not achievable

### Tracing the Optimal Policy

| Access | Hit/Miss? | Evict | Resulting Cache State |

|--------|-----------|-------|-----------------------|

| 0      | Miss      |       | 0                     |

| 1      | Miss      |       | 0,1                   |

| 2      | Miss      |       | 0,1,2                 |

| 0      | Hit       |       | 0,1,2                 |

| 1      | Hit       |       | 0,1,2                 |

| 3      | Miss      | 2     | 0,1,3                 |

| 0      | Hit       |       | 0,1,3                 |

| 3      | Hit       |       | 0,1,3                 |

| 1      | Hit       |       | 0,1,3                 |

| 2      | Miss      | 3     | 0,1,2                 |

| 1      | Hit       |       | 0,1,2                 |

| 6 | hits   |

|---|--------|

| 5 | misses |

Reference Row

0 1 2 0 1 3 0 3 1 2 1

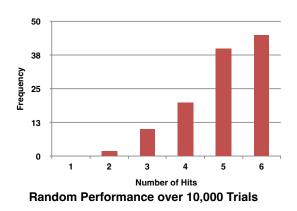

# A Simple Policy: Random

#### • Pick a random page to replace under memory pressure:

- No attempt to do anything fancy

- Performance depends entirely on random chance

| Access | Hit/Miss? | Evict | Resulting Cache State |

|--------|-----------|-------|-----------------------|

| 0      | Miss      |       | 0                     |

| 1      | Miss      |       | 0,1                   |

| 2      | Miss      |       | 0,1,2                 |

| 0      | Hit       |       | 0,1,2                 |

| 1      | Hit       |       | 0,1,2                 |

| 3      | Miss      | 0     | 1,2,3                 |

| 0      | Miss      | 1     | 2,3,0                 |

| 3      | Hit       |       | 2,3,0                 |

| 1      | Miss      | 3     | 2,0,1                 |

| 2      | Hit       |       | 2,0,1                 |

| 1      | Hit       |       | 2,0,1                 |

5 hits 6 misses

187

# Random Performance

• Sometimes, Random is as good as optimal, achieving 6 hits on the example trace.

#### The Exam (all point totals approximate)

- GeekOS and general kernel structure:

- Queueing:

- Characteristics

- Deriving queue lengths

- turnaround time

- etc....

- Paging and memory systems:

- segmentation

- paging

- multi-level page tables

- Paging and swap mechanisms systems:

- victim-replacement policies: LRU, FIFO, OPT

189

# The Exam (all point totals approximate)

- GeekOS and general kernel structure: 10 pts

- Queueing: 25 pts

- Characteristics

- Deriving queue lengths

- turnaround time

- etc.

- Paging and memory systems: 25 pts

- segmentation

- paging

- multi-level page tables

- Paging and swap mechanisms systems: 25 pts

- victim-replacement policies: LRU, FIFO, OPT