### Memory

- 14 Memory API

- 17 Free Space Management

- 13 Address Spaces

- 15 Address Translation

- 16 Segmentation

- 18 Paging

- 19 Translation Lookaside Buffers

- 20 Advanced Paging

- 21 Swapping

- 22 Swapping Policy

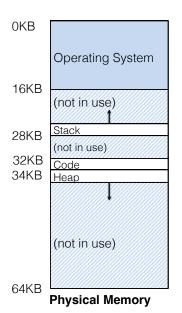

## Issues (still Base and Bounds)

- OS intervenes at three critical junctures:

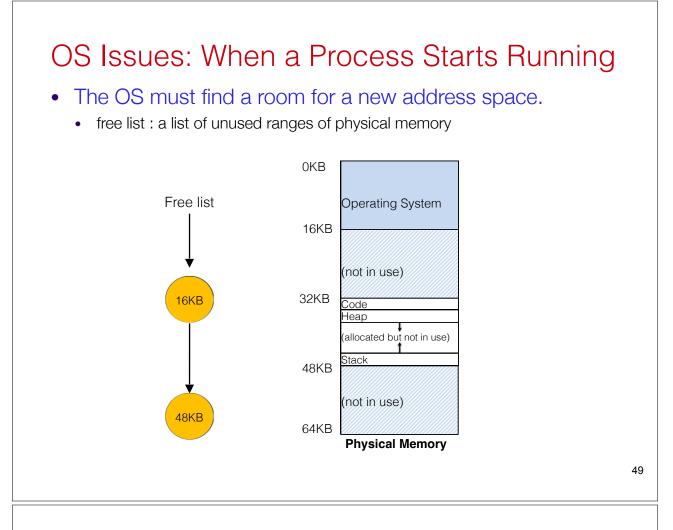

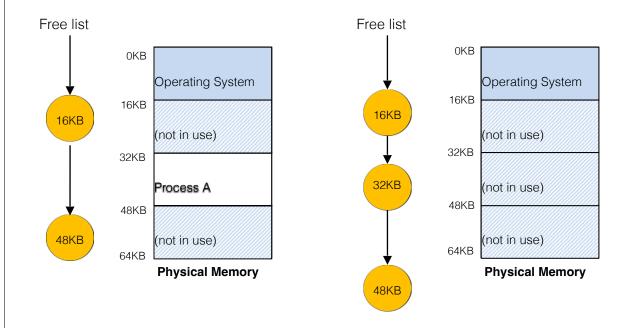

- When a process starts running:

- find space for address space in physical memory

- When a process is terminated:

- reclaims the memory for use

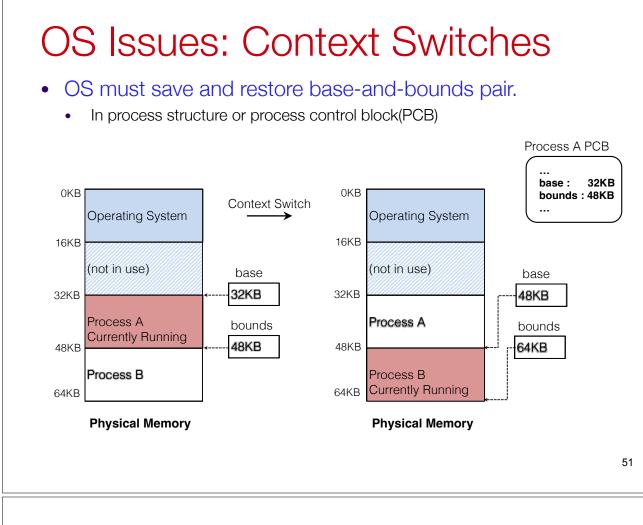

- When context switch occurs:

- Save and store the base-and-bounds pair

## **OS Issues: Process Termination**

• OS must put memory back on the free list.

### Not Always Efficient

- Need big chunk of "free" space

- physically consecutive memory

- Cannot run when address space does not fit into physical memory

#### Memory

- 14 Memory API

- 17 Free Space Management

- 13 Address Spaces

- 15 Address Translation: base and bounds

- 16 Address Translation: Segmentation

- 18 Paging

- 19 Translation Lookaside Buffers

- 20 Advanced Paging

- 21 Swapping

- 22 Swapping Policy

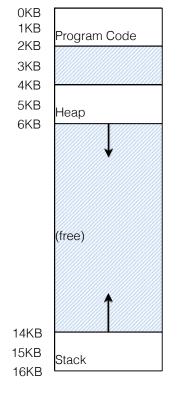

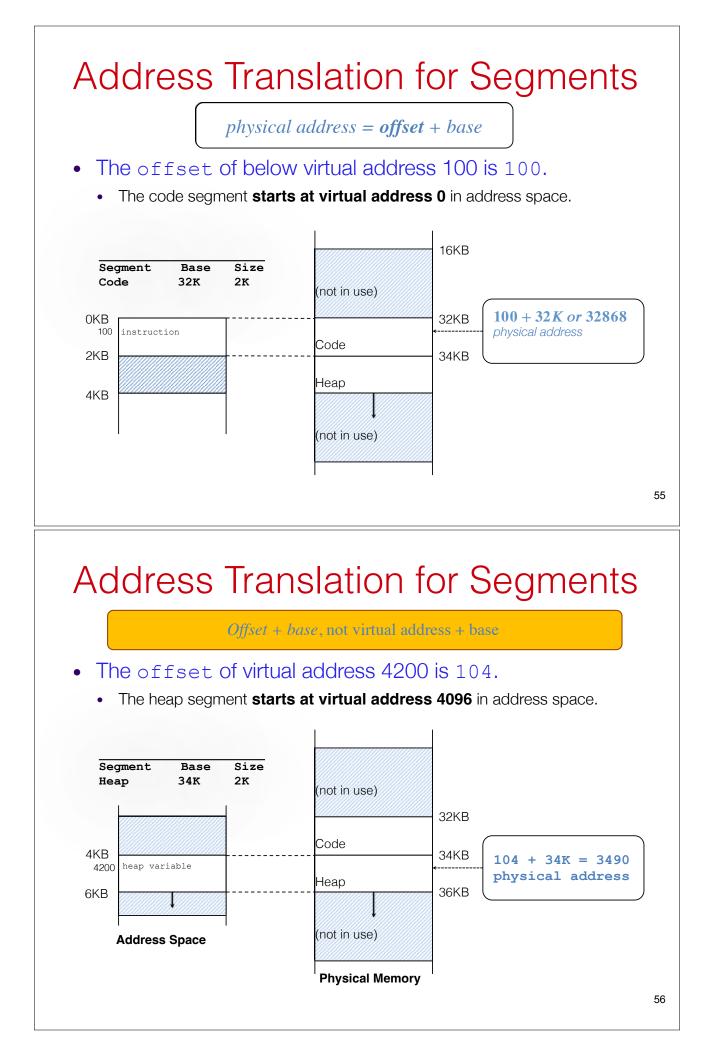

- Segment is a *contiguous* portion of the address space:

- Several types: code, stack, heap, ...

- Segments can be placed anywhere in physical memory.

- Slightly modified base and bounds per segment

| Segment | Base | Size |  |

|---------|------|------|--|

| Code    | 32K  | 2K   |  |

| Heap    | 34K  | 2K   |  |

| Stack   | 28K  | 2K   |  |

|         |      |      |  |

#### Segment Descriptors Explicit approach Chop up the address space into segments based on the top few bits of virtual address. Example: virtual address 4200 (01000001101000) • 13 12 11 10 9 8 17 16 0 0 0 0 0 1 1 0 1 0 0 0 Segment ID Offset Segment bits Code 00 Heap 01 10 Stack 11 57 Segment Descriptors Bits SEG MASK = $0 \times 3000 (110000000000)$ • SEG SHIFT = 12 OFFSET MASK = 0xFFF (0011111111111)

```

1

// get top 2 bits of 14-bit VA

2

Segment = (VirtualAddress & SEG MASK) >> SEG SHIFT

3

// now get offset

4

Offset = VirtualAddress & OFFSET MASK

5

if (Offset >= Bounds[Segment])

6

RaiseException (PROTECTION FAULT)

7

else

8

PhysAddr = Base[Segment] + Offset

9

Register = AccessMemory(PhysAddr)

```

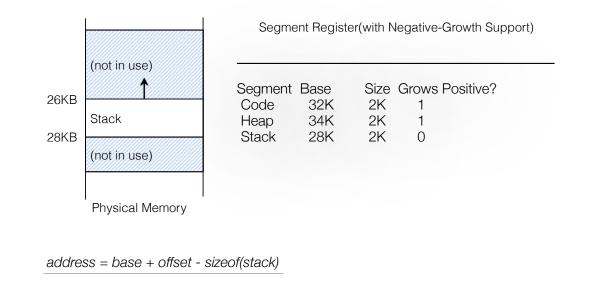

## Referring to Stack Segment

- Stack grows backward.

- Extra hardware support needed.

- The hardware checks which way the segment grows.

- 1: positive direction, 0: negative direction

## Support for Sharing

- Segments can be shared between address spaces

- Code sharing still used

- Need hardware support in form of *protection* bits.

- Bits indicate read, write and execute permissions.

| Segment | Base | Size | Grows Positive? | Protection   |  |  |  |

|---------|------|------|-----------------|--------------|--|--|--|

| Code    | 32K  | 2К   | 1               | Read-Execute |  |  |  |

| Heap    | 34K  | 2К   | 1               | Read-Write   |  |  |  |

| Stack   | 28K  | 2K   | 0               | Read-Write   |  |  |  |

Segment Register Values(with Protection)

59

### Fine-Grained and Coarse-Grained

- Coarse-Grained is small number of segments

- e.g., code, heap, stack.

- Fine-Grained segmentation allows more flexibility

- Hardware-supported segment tables

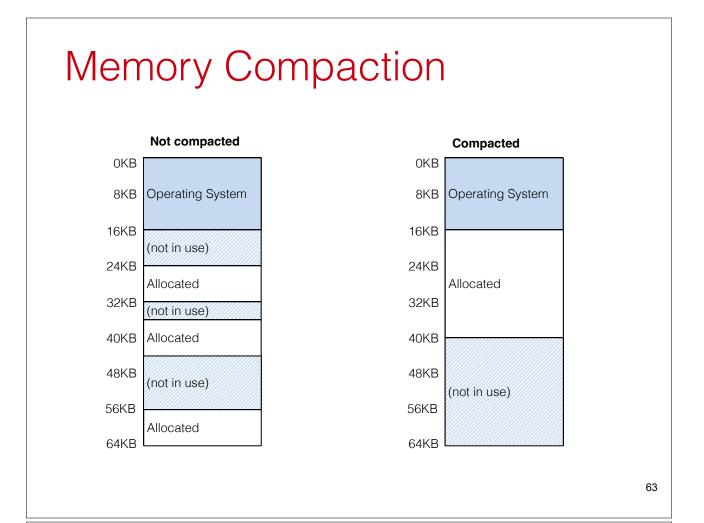

# OS support: Fragmentation

- External Fragmentation:

- Distinct runs of free space in physical memory

- Might be 24KB free, but not in one contiguous segment.

- The OS cannot satisfy the 20KB request.

- Compaction: consolidating existing segments in physical memory.

- Compaction is **costly**.

- **Stop** running process.

- Copy data to somewhere.

- Change segment register value.

### GeekOS

- segmented memory addresses

- 16-bit "segment selector", 32-bit offset

- segment selector has:

- 1 bit: GDT or LDT

- 13 bits: index into GDT or LDT

- 2 bits: protection level of segment

- segment descriptor (from table) has:

- linear base physical address of segment: 32 bits

- limit (size) of segment: 20 bits

- descriptor privilege level (dpl): 2 bits

- type of segment (data, code, system, tss, gate): 4 bits

- present (in-memory): 1 bit

- etc.

# GeekOS

- GDT

- entries point to kernel segments, optionally user segments

- entry 0 (null selector) is not used to access memory

- gdtr register points to the GDT

- LDT similar, but

- points to segments of a single process

- entry 0 can be used

- any number of LDTs can be in memory

- LDTR register points (via GDT) to currently used LDT

## Virtual Memory

- 14 Memory API

- 13 Address Spaces

- 15 Address Translation

- 16 Segmentation

- 17 Free Space Management

- 18 Paging

- 19 Translation Lookaside Buffers

- 20 Advanced Paging

- 21 Swapping

- 22 Swapping Policy

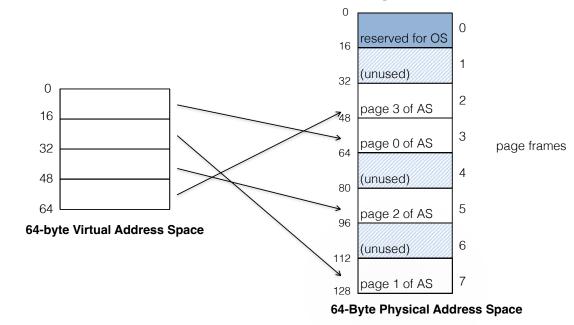

# Paging

- Paging splits address space into fixed-size pages.

- vs segmentation: variable size of logical segments

- Physical memory holding a page is the page frame

- Page table per process

- translates virtual address to physical address.

- Flexibility:

- No assumptions on how heap and stack grow or are used

- Simplicity: ease of free-space management

- All pages and page frames are the same size

- Free lists are easy...

# Paging Example

- 128-byte physical memory with eight 16-byte page frames

- 64-byte address space with 16-byte pages

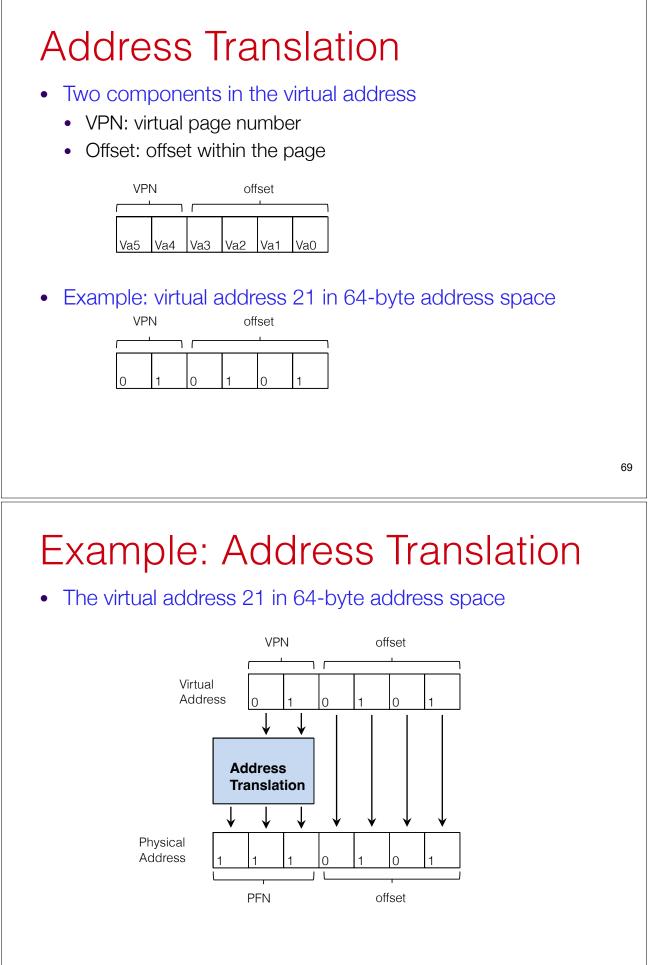

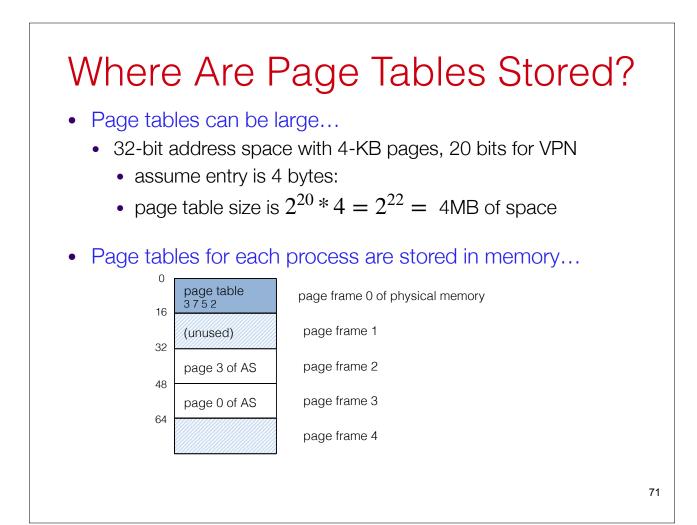

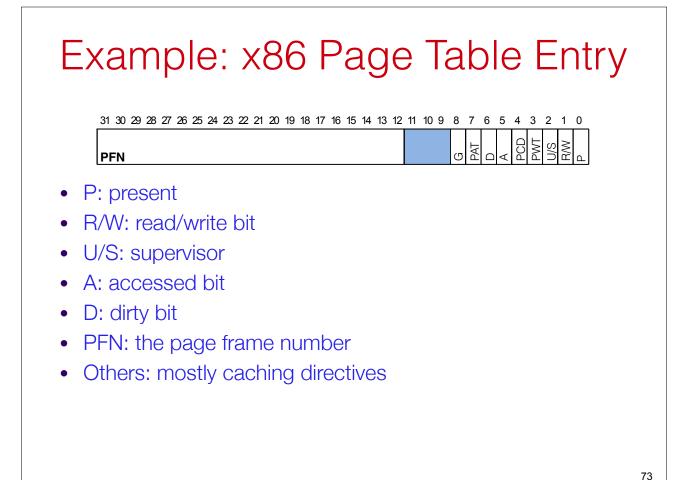

# What Is In The Page Table?

- A page table is just a **data structure** that is used to map the virtual address to physical address.

- Simplest form: a linear page table, an array

- The OS/hardware accesses a page-table entry by indexing into the array by virtual page-number

- Common bits:

- Valid Bit: whether the particular translation is valid.

- Protection Bit: read, write, execute

- Present Bit: in physical memory or swapped out

- Dirty Bit: page modified since it brought into memory

- Reference Bit(Accessed Bit): page has been accessed

## Paging: Too Slow

- To find a location of the desired PTE, the starting location of the page table is needed.

- For every memory reference, paging requires the OS to perform one extra memory reference.

#### Accessing Memory With Paging

```

// Extract the VPN from the virtual address

VPN = (VirtualAddress & VPN MASK) >> SHIFT

// Form the address of the page-table entry (PTE)

PTEAddr = PTBR + (VPN * sizeof(PTE))

// Fetch the PTE

PTE = AccessMemory (PTEAddr)

// Check if process can access the page

if (PTE.Valid == False)

RaiseException (SEGMENTATION FAULT)

else if (CanAccess(PTE.ProtectBits) == False)

RaiseException (PROTECTION FAULT)

else

// Access is OK: form physical address and fetch

offset = VirtualAddress & OFFSET MASK

PhysAddr = (PTE.PFN << PFN SHIFT) | offset

Register = AccessMemory(PhysAddr)

```

75

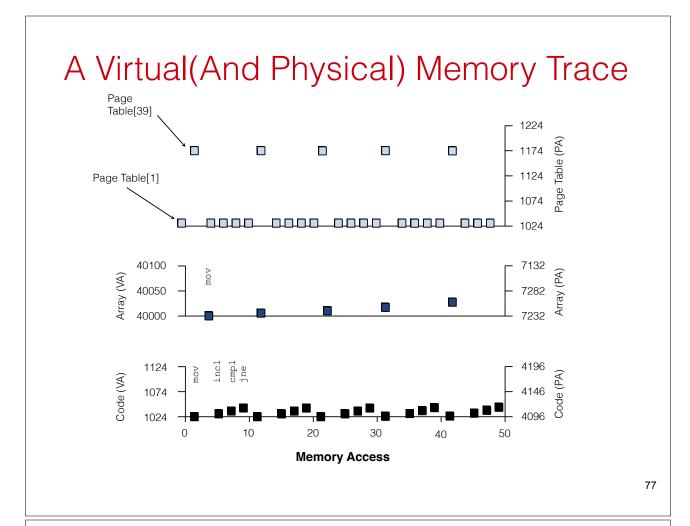

#### A Memory Trace

• Example: A Simple Memory Access

#### Compile and execute

2

3 4

5 6 7

8

9 10

11

12

13

14

15

16

17

18

19

```

prompt> gcc -o array array.c -Wall -o

prompt>./array

```

#### • Resulting Assembly code

```

0x1024 movl $0x0,(%edi,%eax,4)

0x1028 incl %eax

0x102c cmpl $0x03e8,%eax

0x1030 jne 0x1024

```

## Virtual Memory

- 13 Address Spaces

- 14 Memory API

- 15 Address Translation

- 16 Segmentation

- 17 Free Space Management

- 18 Paging

- 19 Translation Lookaside Buffers

- 20 Advanced Paging

- 21 Swapping

- 22 Swapping Policy

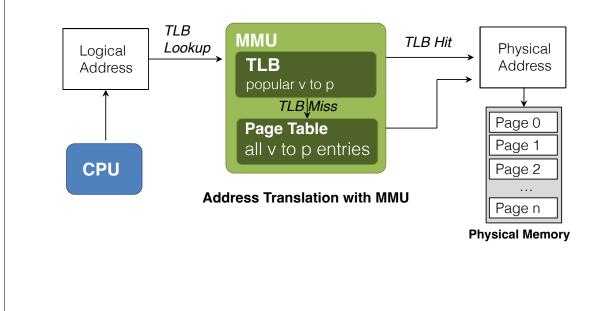

## TLB

- Part of the chip's memory-management unit(MMU).

- A hardware cache of **popular** virtual-to-physical address translation.

TLB Basic Algorithms

- extract the virtual page number (VPN).

- check for hit in the the TLB

- extract page frame number from relevant TLB entry, form desired physical address, and access memory

```

1: VPN = (VirtualAddress & VPN_MASK ) >> SHIFT

2: (Success , TlbEntry) = TLB_Lookup(VPN)

3: if (Success == True) { // TLB Hit

4: if (CanAccess(TlbEntry.ProtectBit) == True ) {

5: offset = VirtualAddress & OFFSET_MASK

6: PhysAddr = (TlbEntry.PFN << SHIFT) | Offset

7: AccessMemory( PhysAddr )

8: } else RaiseException(PROTECTION_ERROR)

```

# TLB Basic Algorithms (Cont.)

- (11-12 lines) The hardware accesses the page table to find the translation.

- (16 lines) updates the TLB with the translation.

```

11:

} else { //TLB Miss

12:

PTEAddr = PTBR + (VPN * sizeof(PTE))

13:

PTE = AccessMemory(PTEAddr)

14:

(...)

15:

} else {

16:

TLB Insert( VPN , PTE.PFN , PTE.ProtectBits)

17:

RetryInstruction()

18:

}

19:}

```

81

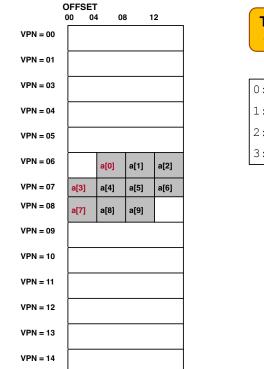

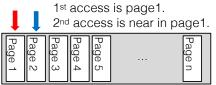

### Example: Accessing An Array

• How a TLB can improve its performance.

| The TLB improves        | performance |  |

|-------------------------|-------------|--|

| due to spatial locality |             |  |

| 0:                   | int sum = $0$ ;                      |

|----------------------|--------------------------------------|

| 0:<br>1:<br>2:<br>3: | <pre>for( i=0; i&lt;10; i++) {</pre> |

| 2:                   | <pre>sum+=a[i];</pre>                |

| 3:                   | }                                    |

3 TLB misses and 7 hits. Thus TLB hit rate is 70%.

## Locality

- Temporal Locality

- An instruction or data item that has been recently accessed will likely be reaccessed soon in the future.

#### Virtual Memory

#### • Spatial Locality

If a program accesses memory at address x, it will likely soon access memory near x.

**Virtual Memory**